PROPERTY AND DESCRIPTION

加拉·安安拉克 公子

# HOW TO USE THE CPS/1 MICRO-COMPUTER SYSTEM

Canadian and Foreign Patents Pending.

| 1   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | General Description of the CPS/1 System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1  |

| 1.2 | Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2  |

| 1.3 | Instruction Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3  |

| 1.4 | Organization and the second se |    |

| 2   | CENTRAL PROCESSOR INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5  |

| 2.1 | Memory Reference Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5  |

| 2.2 | Housekeeping Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7  |

| 2.3 | Accumulator and Working Register Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 3   | PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 |

| 3.1 | Introduction is this sakes and by clomen and to deep a surface best of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16 |

| 3.2 | Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16 |

| 3.3 | Subroutines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19 |

| 3.4 | Looping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20 |

| 3.5 | Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21 |

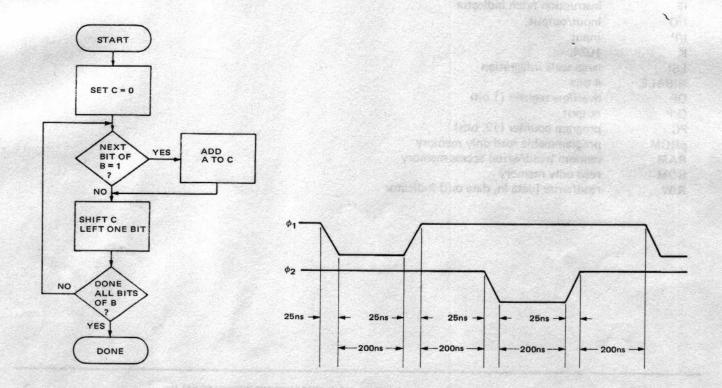

| 3.6 | Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22 |

| 4   | INSTRUCTION TIMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23 |

|     | GLOSSARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24 |

# INTRODUCTION : The second of t

#### 1.1 General Description of the CPS/1 System

The CPS/1 is the first in a series of general purpose microcomputer systems by Microsystems. The system central processor is contained entirely on one MOS LSI integrated circuit chip. System memory, depending on size, is contained on two or more additional LSI chips. The CPU contains two memory pointers: the usual program counter (PC), and a data pointer (DP), which allows logical, as well as physical separation, of program and data. Both the PC and the DP are 12. bits long and can directly address 4096. memory locations. A memory expander chip is available to extend addressing capability to 256K. locations (K = 1024.). Each memory location contains 4 bits of data (one nibble, which is half a byte).

The made in the said has easily visition graphers with the rest and action and year on the form

on little ger to your blots to have set and also you go best you be the release and new your rate accordings.

section. If lamingrayed racing to be a stock meaning that the particular in

THE WASH THE

MICCOL COMPLETER SYST

ASSESS FOR DUCTORS

### 1.1 Continued . . .

The CPU uses a 12. bit address bus and a 4 bit, bi-directional data bus to connect to memory and input/output devices. These two buses, together with the 5 control lines, form a 21. line communications bus (COMBUS). A portion of the memory address space is allocated to input/output devices. Thus the CPU can use all its instructions which normally refer to memory to refer to I/O devices over the COMBUS. The COMBUS can be expanded to handle 8 bits of bi-directional data. This allows straight-forward interfacing of byte-oriented devices. Since each I/O port is a memory location, the interfacing of external devices is greatly simplified.

The processor performs a program by executing instructions fetched from consecutive memory locations as counted by the PC. Following the completion of an instruction, the PC is incremented by 2 or 4, depending on the length of the instruction. Sequential program flow is altered by modifying the PC during an instruction. The CPS/1 allows for conditional, unconditional, and subroutine call types of PC modification.

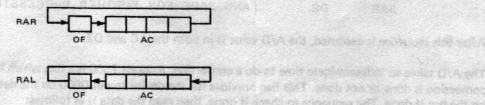

In addition to the PC and DP, two other registers are of interest to the programmer. These are the 4 bit accumulator (AC) and the 1 bit overflow register (OF). Data can be moved into or out of the AC from memory. The contents of a memory location can be ADD'ed or NAND'ed to the AC. The AC and OF can be rotated together left or right. The contents of AC and OF can be tested for various conditions.

A unique feature of the CPS/1 is the set of working registers. There are eight 4 bit data registers and eight 12. bit address registers. These are implemented as part of the memory address space and are external to the CPU chip. Although access speed is not improved over regular memory, addressing overhead is reduced, resulting in shorter instructions. This allows the working registers to be very effective as scratch pad storage to hold such items as intermediate results and loop counts. As an additional convenience, the working registers can be addressed as normal memory locations.

Throughout this document decimal numbers are distinguished from octal numbers by use of periods after decimal numbers. This is the same convention as for CPS/1 Assembler language.

#### 1.2 Addressing

The CPS/I can directly address 4096. nibbles of main memory. The first 32. nibbles must be RAM for implementation of the working data and address registers. The remaining memory space can be used for RAM, ROM or I/O addresses. Memory can be expanded to vertually any size by the use of field switching. The memory is logically divided into 256. nibble pages by the JCDN instructions, which replace the 8 low-order bits of the PC when a jump occurs. Program flow between pages takes place by normal PC incrementing between instructions, or by the exchange jump XPD.

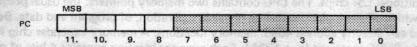

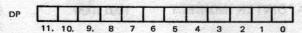

The bits of the registers in the CPS/1 are numbered right to left, starting with 0.

The shaded portion represents the bits replaced by the JCDN instructions.

The shaded bits are those which are replaced by the DP modifier.

OF \_\_\_\_\_ AC \_\_\_\_\_\_\_

#### 1.2 Continued ...

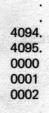

Program execution starts at location 1024. following a system reset. If less than 1024, nibbles of memory are installed, the appropriate location for program start should be assigned to address 1024...

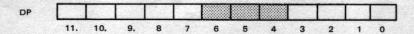

#### 1.3 Instruction Formats

There are two lengths of CPU instructions: 8 bit and 16. bit. Within each length class there are several different formats. The first four bits of each instruction determine the major functions.

#### 1.4 Organization

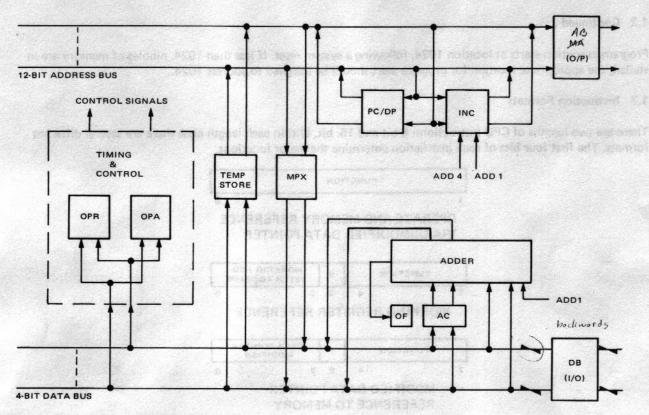

The CPS/1 is organized around two buses, the 4 bit data bus and the 12. bit address bus. Figure 1 shows a block diagram of the CPU. Data and instructions enter the CPU over the data bus. Instructions are stored in OPR and OPA. Data go to temporary storage (temp store) or to the AC. The PC/DP pair and their associated incrementer operate from the 12.bit address bus. The data bus and address bus are buffered off the chip by the data buffer and memory address buffer, respectively.

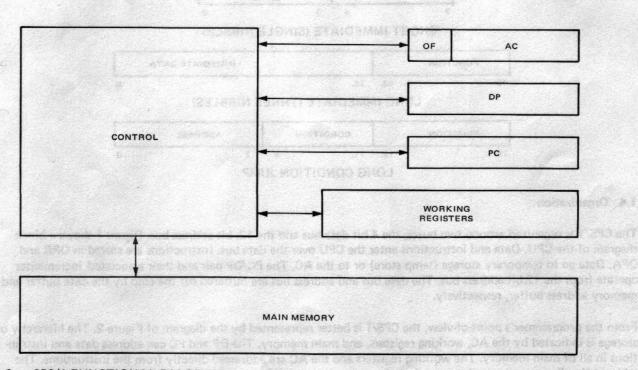

From the programmer's point-of-view, the CPS/1 is better represented by the diagram of Figure 2. The hierarchy of storage is indicated by the AC, working registers, and main memory. The DP and PC can address data and instructions in all of main memory. The working registers and the AC are addressed directly from the instructions. The adder/shifter/incrementer in the control section operate on the AC and on memory or register data.

FIG. 1. CPS/1 BLOCK DIAGRAM

INCHASHUS.

FIG. 2. CPS/1 FUNCTIONAL DIAGRAM

#### 2 CENTRAL PROCESSOR INSTRUCTIONS

This chapter describes the instruction set of the CPS/I and the effect of each instruction on the CPU registers and memory. For ease of presentation, the instructions are grouped by function. Timing is given for each instruction in clock cycles (memory cycles), as explained in Section 4. The mnemonics given in the boxes with each instruction are those recognized by the assembler (CPAL/I) with two exceptions: JCDN and OPR which are not, themselves, instructions but generic terms for classes of instructions. Where appropriate, examples of instruction usage and special techniques of a very general nature are included. More detailed programming examples are given in Section 3.

In the instruction descriptions, these conventions are used:

| XXX  | represents immediate data or DP modifier bits, |

|------|------------------------------------------------|

| DDD  | represents a working data register (D0-D7),    |

| AAA  | represents a working address register (A0-A7), |

| CCCC | are the condition codes for jumps, and         |

| PPPP | is the operate micro-code.                     |

The following general rules can be stated about the instructions:

- a) The overflow register (OF) is affected only by instructions which add to, increment, or rotate the accumulator, and those instructions which name the OF explicitly.

- b) The modified-data-pointer instruction replaces bits 6-4 only for the duration of the instruction. At the end of the instruction the DP resumes the value it had at the beginning of the instruction.

c) Incrementing the data pointer and program counter cause wrap-around at address 4095.. The carry is discarded and the register is set to 0.

THE THE PROPERTY OF THE STATE OF THE PARTY.

VE CAPPIDENT ATAC HELD SA CALLE

ling and to this self that I were to take the construction of this majores to cover some constitution in Artist I reclaim a

### 2.1 Memory Reference Instructions

Memory references in the CPS/1 are made using the data pointer (DP). The value of the 12. bits in the DP specifies a memory location or the first of several consecutive locations. The DP is not automatically incremented following a reference; therefore, the program is free to modify the DP as desired.

Burnande this year on enterior state out without during production and that

service or included of Commences of the instrument of the instrume

Many of the memory reference instructions allow temporary modification to the DP. In these instructions the modification is in effect only during the fetching of the operand from memory. The modification is done by replacing bits 6-4 in the DP by the modifier from the instruction.

## USE OF THE CPS/1 SYSTEM **BULLETIN 50001**

2.1.1 Programming Conventions. Instructions which do not modify the DP require only the operation code to be specified. Instructions which modify the DP require the modifying bits to be present in the operand field. Since the modifier is 3 bits, the number must be in the range 1-7 (0 is no modification). These bits are indicated by XXX in the instruction description.

## 2.1.2 LOAD and STORE Instructions.

LAD LOAD ACCUMULATOR

00011000

3 cycles 2 nibbles

The data at the memory location specified by the data pointer are loaded into the accumulator. The previous contents of the accumulator are lost.

LAM

LOAD ACCUMULATOR (MODIFIED)

00011XXX

3 cycles

2 nibbles

The data pointer is temporarily modified by replacing bits 6-4 with XXX from the instruction. The data at the memory location specified by the modified data pointer are loaded into the accumulator. The previous contents of the accumulator are lost.

SAD STORE ACCUMULATOR 00101000

3 cycles

2 nibbles

The accumulator is stored in the memory location specified by the data pointer. The contents of the accumulator are not affected.

LDID

LOAD DATA POINTER INDIRECT

10011000

terior) as 4.7 cas of popular or unit of special or side properties of consideration

5 cycles

2 nibbles

The data pointer is loaded with the three memory locations specified by the data pointer. The initial value of the data pointer is lost. The first location from which the data pointer is loaded MUST have an address whose two low order bits are 01.

Consider a stack of addresses which begin at location 425. To retrieve the first address from the top of the stack the following instructions are executed:

> LDI 425 LDID

; LOAD DP IMMEDIATE WITH STACK ADDRESS

FETCH FIRST ADDRESS FROM STACK

LAD

LOAD AC WITH DATA SPECIFIED BY

FIRST ADDRESS OF STACK

Note that the instructions which modify the data pointer do not add the modifier to the DP, but rather replace bits 6 - 4. This provides for accessing arrays of data without changing the DP. An example is two 16 digit decimal registers located at addresses 400 and 420, respectively. The following instructions load the first digit from each register into the accumulator: processed viscours of the state of another located extensions from the state of an entreed on

act chartestant areas et file of a stromeshill on vision and would are to print our roles vaccount at the world as we are a street to enter my development of the present of the present of the machine of a methodistical

### USE OF THE CPS/1 SYSTEM BULLETIN 50001

#### 2.1.2 Continued . . .

| LDI       | 400 | SET DP TO FIRST REGISTER               |

|-----------|-----|----------------------------------------|

| •         |     |                                        |

| •         |     | 一、原理的产品。1955年的自由的发生,指导的一种特别的企业的发展的主义。  |

| LAD       |     | ;LOAD FIRST DIGIT OF FIRST REGISTER,   |

| • Maria 1 |     | ; EFFECTIVE ADDRESS IS 400 (100000000) |

| wilden a  |     |                                        |

| LAM       | 1   | ;LOAD FIRST DIGIT OF SECOND REGISTER,  |

|           |     | ; EFFECTIVE ADDRESS IS 420 (100010000) |

| •         |     |                                        |

| SAD       |     | TRANSFER DIGIT TO FIRST REGISTER       |

|           |     |                                        |

Thus, arrays of data can be stepped through without the need to constantly save and restore the data pointer.

#### 2,1.3 Count Instructions.

| ISZD | INCREMENT AND SKIP IF ZERO | 01101000 | 4 cycles  |

|------|----------------------------|----------|-----------|

|      |                            |          | 2 nibbles |

The contents of the memory location specified by the data pointer are incremented by 1. If the increment results in zero, the PC is incremented by 4, skipping 4 locations (one 4 nibble instruction or two 2 nibble instructions). The OF is not affected.

| ISZM      | INCREMENT AND SKIP IF ZERO | 01101XXX        | 4 cycles  |

|-----------|----------------------------|-----------------|-----------|

| inlays do | (MODIFIED)                 | CASTAIN MATAGER | 2 nibbles |

The data pointer is temporarily modified by replacing bits 6 – 4 with XXX from the instruction. The contents of the memory location specified by the data pointer are then incremented by 1. If the increment results in zero, the PC is incremented by 4, skipping 4 locations. (One 4 nibble instruction or two 2 nibble instructions.) The OF is not affected.

The two previous instructions are used to count loop iterations or to successively modify a nibble for a series of operations. Consider a block of 12, locations which contains data from which it is desired to calculate a check sum (the sum of all items without regard to carry overflow). The following instructions can achieve this operation:

|       | LAI<br>SAD       | -12           | ;LOAD COUNT OF NEGATIVE 12<br>;STORE IT @DP                                |

|-------|------------------|---------------|----------------------------------------------------------------------------|

| LOOP: | inis sortis mili | evisit, herva | PROCESSING                                                                 |

|       | I SZD<br>JMP     | LOOP          | ; INCREMENT COUNT, SKIP IF ZERO<br>; NOT DONE, RETURN FOR MORE PROCESSING. |

## 2.2 Housekeeping Instructions

These are the instructions which affect the CPU registers other than the accumulator (AC). They are used to control program flow by affecting the program counter (PC) and to control data flow by affecting the data pointer (DP). There are instructions for jumping, testing, subroutine calling, incrementing and decrementing DP, and causing program delays. The only instructions in this group which require operands are LDI and jump.

#### USE OF THE CPS/I SYSTEM **BULLETIN 50001**

### 2.2 Continued . . .

NOP2

TWO NIBBLE NO OPERATION

00000000

3 cycles

2 nibbles

The program counter is advanced 2 nibbles. None of the registers are affected.

NOP4

FOUR NIBBLE NO OPERATION 111000000000000

5 cycles

4 nibbles

The program counter is advanced 4 nibbles. None of the registers are affected.

The NOPs are used to cause program delays and to pad a program for address alignment or provide skip protection. The program sequence below uses the ISZ instructions, but does not want the skip to affect the logic of the program (modulo 16. counter, for instance). The NOP4 is used in place of the normal JMP following the ISZ.

DAN SINGERO LINE EVEL VICTOR DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DESCRIPTION DE LA PROPRIE DE LA PROPR

the content of the between both as the court of the court are both to be the both and the court of the second of the court of the court

ISZD NOP4

INCREMENT COUNT

DO NOTHING

SAR NEXT INSTRUCTION AFTER ISZD

The sequence has the same effect if the ISZ operand is either zero or non-zero.

LDI

LOAD DATA POINTER IMMEDIATE

1101XXXXXXXXXXXXX

5 cycles 4 nibbles

The X-bits from the instruction replace the current data pointer. This instruction is used to initially set the DP to a known value. Note that the DP is undefined following a system reset.

IDP

**INCREMENT DATA POINTER**

3 cycles 2 nibbles

The data pointer (DP) is incremented by 1. If the DP is 7777 before IDP is executed, the value after incrementing is 0000 (the incrementing is done modulo 4096.). The OF is not affected,

DDP

DECREMENT DATA POINTER 10100000

5 cycles 2 nibbles

The data pointer (DP) is decremented by 1. If the DP is 0000 before DDP is executed, the value after decrementing is 7777. The OF is not affected.

XPD EXCHANGE PROGRAM COUNTER

00001111

and the FLL on stream of separation many many fift of motorstand vino set a very manager

3 cycles

AND DATA POINTER

2 nibbles

The contents of the data pointer (DP) and the program counter (PC) are swapped. The next instruction executed is taken from the new PC.

This are the instruction which affile the QUI register than that the continue and unit with an are the property of the continue and the continue are the continue and the continue are the continue and the continue are the contin CHGA restricted after the processor of each even to a contract of the contract and address the even manager of ataense bink. 10 septime messe, brinspirermoteri ginder untrumpten primer primer sel pepitagnasi me speri.

#### 2.2 Continued . . .

10) tarage adhes

OF Interest Description

The XPD instruction is the subroutine-call instruction. The normal sequence is as follows:

| LDI            | SUB1 | JLOAD ADDRESS OF SUBROUTINE |

|----------------|------|-----------------------------|

| XPD            |      | SEXCHANGE PC & DP           |

| Particular Con |      | 生物,可以使用的一种的一种的一种的一种。        |

Arguments are normally passed to the subroutine via the working registers. Return is made from the subroutine by simply giving another XPD, which returns control to the instruction following the calling point. If the DP is required in the subroutine, it can be saved in a working register. Note that the call sequence is pure, (i.e., re-entrant) since no memory is modified.

letter den Miller i Genego en entraffrect et en over gran brokk trokke trok fall det Gillan to den bliskere

JCDN JUMP ON CONDITION GROUP 1110CCCCXXXXXXXX 5 cycles 4 nibbles

CONSTRUCTOR

EDA KALLO SIMBONIO IN ACIDI

tels antifered water it south will

medium tion Consider two sain

If the conditions specified by bits CCCC are satisfied, then bits 7 - 0 of the program counter (PC) are replaced by the X-bits of the instruction. If the conditions are not satisfied, the effect is an NOP.

Special mnemonics are assigned to the conditions for jumps, as follows:

| CONDITION       | LETTER                 |  |

|-----------------|------------------------|--|

| OF = 1 00017010 | T (true)               |  |

| OF = 0          | F (false)              |  |

| AC >9           | G (greater than)       |  |

| AC ≤ 9          | L (less than or equal) |  |

| AC = 0          | Z (zero)               |  |

| AC ≠ 0          | N (non-zero)           |  |

This can be combined to yield the 16. values of the 4 bit condition field, as follows:

| cccc | MNEMONIC | CONDITIONS                      |

|------|----------|---------------------------------|

| 0    | NOP4     | never jump                      |

| 1    | JG       | AC > 9.                         |

| 2    | JZ       | AC = 0                          |

| 3    | JGZ      | AC > 9. OR, AC = 0              |

| 4    | JT       | OF = 1                          |

| 5    | JTG      | OF = 1 OR, AC > 9.              |

| 6    | JTZ      | OF = 1 OR, AC = 0               |

| 7    | JTGZ     | OF = 1 OR, AC > 9. OR, AC = 0   |

| 8    | JMP      | always jump                     |

| 9.   | JL STATE | AC ≤ 9.                         |

| 10.  | JN       | AC≠0                            |

| 11.  | JLN      | AC ≤ 9, AND, AC ≠ 0             |

| 12.  | JF       | OF = 0                          |

| 13.  | JFL      | OF = 0 AND, AC ≤ 9.             |

| 14.  | JFN      | $OF = 0$ AND, $AC \neq 0$       |

| 15.  | JFLN     | OF = 0 AND, AC ≤ 9, AND, AC ≠ 0 |

### 2.2 Continued . . .

The jump is an "on page" jump, not a relative jump. For this purpose the memory is divided into pages of 256. locations, i.e., page boundaries have 8 low-order zeros in their addresses. Since the jump consists of replacing the low-order bits of the PC, the JMP instructions cannot cross these page boundaries, not even if the JMP is executed on the last location of a page.

The conditional jumps are used to alter program flow in response to data-dependent conditions. As an example, consider a loop of instructions to be executed until the overflow register (OF) is set or the accumulator is zero as follows:

LOOP:

INSTRUCTIONS FOR PROCESSING

JDATA...

JTZ

DO AGAIN IF NOT SATISFIED

### 2.3 Accumulator and Working Register Instructions

LOOP

This group of instructions references the accumulator (AC) and/or the 16. working registers. There is one arithmetic set of instructions and one logical set which reference the AC and memory.

2.3.1 Programming Conventions. Where a working register is required it is supplied by the programmer as an operand. The 8 data registers are named D0 through D7, and the 8 address registers, A0 through A7. The working registers can also be addressed via the data pointer (DP).

#### 2.3.2 Arithmetic Instructions,

ADD

ADD MEMORY TO ACCUMULATOR

01011000

4 cycles 2 nibbles

The data at the memory location specified by the data pointer are added to the contents of the accumulator (AC). The original contents of AC are lost. If there is a carry from the high order bit of the AC, the overflow register (OF) is unconditionally set to 1.

ADM

ADD MEMORY TO ACCUMULATOR (MODIFIED)

01011XXX

4 cycles 2 nibbles

The data pointer (DP) is temporarily modified by replacing bits 6-4 with XXX from the instruction. The data at the memory location specified by the modified DP are added to the contents of the accumulator (AC). The original contents of the AC are lost. If there is a carry from the high order bit of the AC, the OF is unconditionally set to 1.

ADR

ADD REGISTER TO ACCUMULATOR

01010DDD

F.197

4 cycles 2 nibbles

The data from a working data register DDD is added to the contents of the accumulator (AC). The original contents of AC are lost. If there is a carry from the high order bit of AC, the OF is unconditionally set to 1.

The ADD instructions can be used, in conjunction with the conditional jump instructions, to do binary and decimal arithmetic. Consider two binary, multiple-precision numbers, A and B, each 12. nibbles (48. bits) long, and stored at 1000 and 1020, respectively. The following routine adds B to A and stores the result C (located at 1040 in memory).

and industrial to the property of the first and the second of such as the property of the second

Liberal SEC

### 2.3.2 Continued . . .

```

;LOAD DP WITH ADDRESS OF 'A'

LDI

1000

SET UP LOOP COUNTER

LAI

-12

IN WORKING REGISTER D2

SAR

D2

CLEAR OVERFLOW REGISTER

CLF

CLEAR AC, LOAD CARRY INTO AC

LOOP:

CLARL

ADD

; ADD IN A NIBBLE OF 'A'

; ADD IN A NIBBLE OF 'B'

ADM

SAM

STORE RESULT NIBBLE, CARRY IN OF

IDP

INCREMENT DP TO NEXT NIBBLE

ISER

DONE YET?

JMP

LOOP

;NO - RETURN FOR NEXT NIBBLE

JT

OVFL

; YES, GO TO OVFL IF OVERFLOW ...

```

In this example, if a carry occurs in the first ADD, none can occur in the ADM, because the AC is zero.

The same routine as just described, with slight modification can perform decimal addition. Assuming D3 contains the constant 6, the following instructions can perform this task:

LARGE STORE TREETED

TIES about

| LOOP:          | CLARL              |              | CLEAR AC, LOAD CARRY                                                                                           |

|----------------|--------------------|--------------|----------------------------------------------------------------------------------------------------------------|

|                | ADD                |              | ;ADD DIGIT OF 'A'                                                                                              |

|                | ADM                | 1            | ; ADD DIGIT OF 'B'                                                                                             |

|                | JFL                | STORE        | SKIP NEXT INSTRUCTION IF AC <ok= &="" 9="" of="0&lt;/td"></ok=>                                                |

|                | ADR                | D3           | ;ADD CORRECTION                                                                                                |

| STORE:         | SAM                | 2            | STORE RESULT DIGIT                                                                                             |

| A SE TAMONO TH | 17 • National 2011 | of Phone and | or modern a feature reader for the configuration and it is comparable to the parameter of the parameter of the |

The number 6 is added because the AC overflows at 15, rather than at 10.. If the result is greater than 9, a carry should result. The carry is forced by adding 6.

but the total and the second expension with the following an according

Consider 9, + 9, = 18., which is 8 with a 1 carry:

| 1001   | 9.  |

|--------|-----|

| +1001  | +9. |

| 1 0010 | 12. |

| +0110  | +6  |

| 1 1000 | 18. |

to arrive a consistent of a ROCA in terrementation of a consistent formalist in more than

Subtraction is done by complementing the subtrahend and adding. The 1's complement is used for binary, and the 9's complement for decimal.

#### 2.3.2 Continued : . .

The use of 1's complement arithmetic allows for simple complementing and carry propagation as in addition. Using the previous example of A and B, together with C, C is calculated as: C = A -B, to 48. bits of precision, by executing the following instructions:

ASTROPHENING TO THE STATE OF

```

L00P1:

LAM

GET NIBBLE OF 'B'

COMPLEMENT IT

COM

SAR

D4

SAVE IT IN A WORK REGISTER

CLARL

;LOAD CARRY FROM PREVIOUS NIBBLE

ADD NIBBLE OF 'A'

ADD

JADD COMPLEMENT OF 'B'

ADR

SAM

STORE RESULT IN 'C'

; INCREMENT DP TO NEXT NIBBLE

IDP

D2

DONE YET?

ISZR

LOOP1

;NO, DO NEXT NIBBLE

JMP

JF

DONE

DONE IF NO CARRY

; ADD ONE TO 'C'

1040

LDI

SET UP COUNT

LAI

-12

SAR

DS

; IN D2

CLF

; CLEAR OF

GET CARRY

L00P2:

CLARL

; ADD NIBBLE OF 'C'

ADD

; AND STORE RESULT

SAD

INCREMENT DP FOR NEXT

IDP

ISZR

D2

DONE ?

.IMP

LOOP2

;NO, DO MORE...

DONE:

```

The previous instructions first calculate the 1's complement of B, saving it in a working register. The process then continues as in addition. After the addition is finished, the result C is incremented at LOOP 2 if there is a carry at the end of the addition.

Panyo Linkan syote (

Decimal subtraction is done the same way except for the calculation of the 9's complement. The 9's complement is formed for each digit by subtracting the digit from 9. (or by adding 7, which is the 2's complement of 9, and then forming the 2's complement of the addition). Thus decimal subtraction can be done by replacing the first 6 instructions in the above example with the following instructions:

```

CLARL ;SAVE CARRY

LAR D6 ;LOAD -9

ADD 1 ;ADD DIGIT OF 'B'

COM ;COMPLEMENT AND

IAC ;INCREMENT TO SET 9'S COMPLEMENT

CLF ;CLEAR OF

ADR ;ADD PREVIOUS CARRY

```

A ST SECURIT COURSE SECURITION OF WORLD OFF

2.3.2 Continued . . .

ADD JADD DIGIT OF 'A'

JFL DONE SKIP IF NO CARRY

ADR D3 JADD CORRECTION

DONE: •

and inserting between the ADD and SAD in LOOP 2 the following:

JFL NOC JCHECK IF CARRY ADR D3 JADD CORRECTION

2.3.3 Logical Instructions.

NAD NAND MEMORY WITH ACCUMULATOR `01001000 4 cycles 2 nibbles

The data at the memory location specified by the data pointer are NAND'ed with the contents of the accumulator (AC). The original contents of the AC are lost and are replaced by the NAND'ed result.

NAM NAND MEMORY WITH 01001XXX 4 cycles ACCUMULATOR (MODIFIED) 2 nibbles

The data pointer (DP) is temporarily modified by replacing bits 6 - 4 with XXX from the instruction. Then a NAD is executed with the modified DP.

NAR NAND REGISTER WITH 01000DDD 4 cycles

ACCUMULATOR 2 nibbles

The data from working register DDD are NAND'ed with the contents of the accumulator (AC). The original contents of the AC are lost and are replaced by the NAND'ed result.

The NAND instruction provides the programmer with a single logical instruction which can easily provide the AND and OR functions,

| INPUT | AND | OF |

|-------|-----|----|

| 00    | 0   | 0  |

| 01    | 0   | 1  |

| 10    | 0   | 1  |

| 11    | 1   | 1  |

These functions can be computed directly by the following algorithms:

| FUNCTION | DEFINITION | ALGORITHM                 |  |

|----------|------------|---------------------------|--|

| AND      | A·B        | COMPLEMENT OUTPUT OF NANI |  |

| OR       | Ā·B        | COMPLEMENT INPUTS TO NAND |  |

#### 2.3.3 Continued . . .

The following examples illustrate the use of these algorithms.

**EXAMPLE 1: AND memory with AC**

NAD COM SNAND MEMORY TO AC

COMPLEMENT TO GET AND

EXAMPLE 2: OR memory with AC

COM SAR

3 COMPLEMENT AC

SAVE IT

LAD COM

LOAD ARGUMENT COMPLEMENT IT

NADR

; NAND TO GET 'OR'

2.3.4 Working Register Instructions.

LAR

LOAD ACCUMULATOR FROM REGISTER

00010DDD

1

3 cycles

2 nibbles

The data from working data register DDD is loaded into the accumulator (AC).

STORE ACCUMULATOR IN

2 nibbles

The contents of the accumulator (AC) are stored in working data register DDD. The AC is not affected.

LAI

LOAD ACCUMULATOR IMMEDIATE 0111XXXX

and focus powolfer set he strong becomes at his sentimor entit.

4 cycles

2 nibbles

The four bits XXXX from the instruction are loaded into the accumulator.

REGISTER

The LAI instruction is useful for loading loop counts. The XXXX bits can be a 2's complement number which is incremented to zero. The following instructions illustrate this method:

metrica lengua est plum metricalam and to emission est to the CEAM and OCE along recommendam medicals of t

SET UP COUNTER (1011) -5 LAI IN DATA REGISTER Ø SAR DØ

TOP:

; PROCESSING

ISER DØ TOP SINCREMENT & SKIP IF ZERO

JMP

MOSTIMITSO

#### 2.3.4 Continued . . .

LDR LOAD DATA POINTER FROM

REGISTER

REGISTER

10010AAA

5 cycles 2 nibbles

The address from working address register AAA is loaded into the data pointer (DP).

SDR

STORE DATA POINTER IN

10000AAA

5 cycles 2 nibbles

The contents of the data pointer (DP) are stored in working address register AAA. The DP is not affected.

SIDR

STORE INCREMENTED DATA POINTER IN REGISTER

10001AAA

5 cycles 2 nibbles

The data pointer (DP) is incremented by 1, then stored in working address register AAA. The incremented DP is still available to the program. Incrementing a DP containing all 1's yields all 0's.

ISZR

INCREMENT AND SKIP IF ZERO REGISTER

01100DDD

4 cycles

2 nibbles

is 1111

The working data register DDD is incremented by 1. If the result of the increment is zero (was all 1's), the next 4 nibbles of program are skipped.

OPR

What are better the interest of

ARITHMETIC OPERATE GROUP

**0011PPPP**

3 cycles

2 nibbles

This set of instructions operates on the accumulator (AC) and the overflow registers (OF). Each instruction performs one or more functions. The following table gives the value of PPPP, the mnemonic for that value (for use with the assembler) and the actions executed.

|                        | PPPP | MNEMONIC | DESCRIPTION                     |

|------------------------|------|----------|---------------------------------|

|                        | 0    | СОМ      | complement AC                   |

|                        | 1    | RAR      | rotate OF and AC right one bit  |

|                        | 2    | RAL      | rotate OF and AC left one bit   |

|                        | 3    | IAC      | increment AC by 1, OF set if AC |

|                        | 4    | CLA      | clear AC                        |

|                        | 5    | CLARR    | CLA then RAR                    |

| Marco elgines          | 6    | CLARL    | CLA then RAL                    |

| në trem be ade ny      |      | STA      | set AC = 0001                   |

| a Mokron ent viga      | 8    | CLF      | clear OF                        |

| dy loci kesseninke     | 9.   | CLFRR    | CLF then RAR                    |

| A partials no sta      | 10.  | CLFRL    | CLF then RAL                    |

|                        | 11.  | IACCF    | IAC then CLF                    |

|                        | 12.  | STF      | set OF = 1                      |

| EMPLY SALE OF THE SALE | 13.  | STFRR    | STF then RAR                    |

|                        | 14.  | STFRL    | STF then RAL                    |

|                        | 15.  | IACSF    | IAC then STF                    |

#### USE OF THE CPS/I SYSTEM BULLETIN 50001

#### 2.3.4 Continued . . .

The sequence to form the 2's complement of two numbers is as follows:

COM

COMPLEMENT AND

IAC

; INCREMENT. (OF DESTROYED)

To save the contents of the OF:

CLARL

CLEAR AC AND ROTATE IN OF

SAR

DØ

STORE AC

To retrieve the contents of the OF:

LAR

DØ

LOAD OF INTO AC

CLFRR

ROTATE BACK INTO OF (CLF CLEARS AC)

to real suitable works as of house etc. 1905 the about the line of

a Vincethia & I la eni nationo 90 a pormomento i ribogo Vincet e del colo de la compositione del composition

#### 3 PROGRAMMING

#### 3.1 Introduction

This section covers in detail the techniques of programming the CPS/1 to perform particular tasks. Emphasis is placed on those unique features of the CPS/1 which are useful in micro-systems. Throughout the following discussions the mnemonics given in Section 2 are used to identify the instructions. The examples given are as processed by CPAL/1, the CPS/1 assembler.

When the CPS/1 is initialized (reset), the only register defined is the program counter (PC). The PC is set to 2000 and program execution is initiated. From this point on the instructions are executed sequentially unless modified by a jump or subroutine call.

# 3.2 Input/Output

Bringing data into the CPS/1 is greatly simplified over most other mini/micro-systems. Each external device connected to the CPS/1 is assigned (responds to) one or more addresses in the memory space. For example, consider an analog to digital converter (A/D) which responds as follows: each time address 6000 is sent down the address bus, the A/D places the numeric (4 bit) representation of its analog input on the data bus. This is simply the action of a normal memory location being read. Sending out the address results in the data in the location addressed being placed on the data bus. Each address must have only one device associated with it; a memory location and an A/D on the same address would cause errors.

The instructions required to read the A/D (input a value from the A/D) into the AC and also save it are as follows:

LDI 7001

;LOAD DP WITH A/D ADDRESS

LAD

;LOAD AC WITH A/D VALUE

SAR D2

; AND SAVE FOR FURTHER PROCESSING

After this sequence is executed, the A/D value is in both the AC and D2.

The A/D takes an indeterminate time to do a conversion. Address 7000 is a flag which indicates whether the conversion is done or not done. This flag provides for the device to put 0000 on the data bus if not done and 1111 on the bus if done. The sequence to check if done, then read the data is as follows:

#### 3.2 Continued . . .

| TEST: | LDI       | 7000 | ;LOAD DP WITH ADDRESS OF FLAG<br>;FETCH FLAG                                                                                                                                                                                                                                                                                               |

|-------|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | JE<br>IDP | TEST | JUMP BACK IF NOT DONE. JINCREMENT DP TO ADDRESS OF VALUE                                                                                                                                                                                                                                                                                   |

|       | LAD       | D2   | ;LOAD VALUE<br>;SAVE IT                                                                                                                                                                                                                                                                                                                    |

|       |           |      | 전 병원에 보면 한 경기 원인 경기 전 경기 등을 받는 것이 되었다. 그 사람들은 그리고 있는 것이 없는 것이 되었다. 그리고 있는 것이 없는 것이 없는 것이 없는 것이 없는 것이다. 그런 것이 없는 것이 없는 것이 없는 것이다. 그런 것이 없는 것이다면 없는데 없는데 없어요. 그런데 없는데 없는데 없는데 없는데 없는데 없는데 없는데 없는데 없는데 없는 |

This program stays in the test loop (LAD, JZ) until the A/D signals ready by sending a non-zero flag.

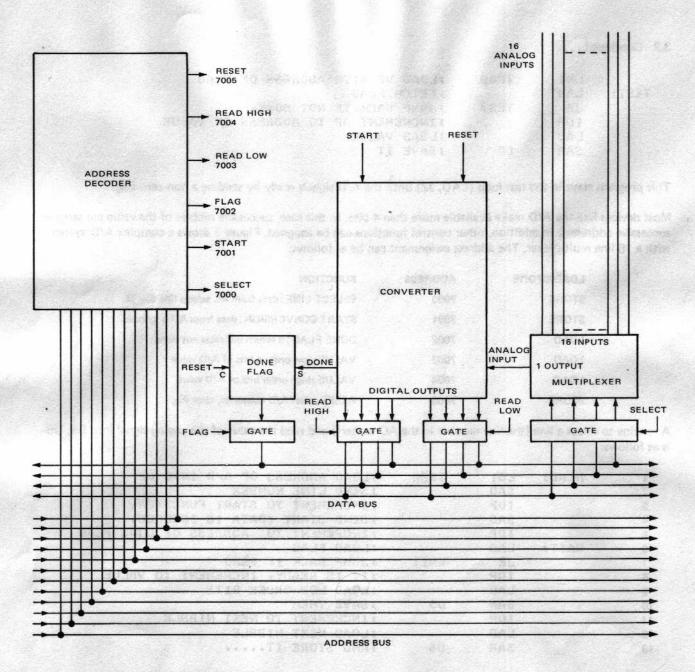

Most devices like the A/D make available more than 4 bits. In this case, successive nibbles of the value are assigned successive addresses. In addition, other control functions can be assigned. Figure 3 shows a complex A/D system with a 16-line multiplexer. The address assignment can be as follows:

| LOAD/STORE | ADDRESS | FUNCTION                                        |

|------------|---------|-------------------------------------------------|

| STORE      | 7000    | SELECT LINE : data from AC selects line 0 - 15. |

| STORE      | 7001    | START CONVERSION : data from AC is ignored      |

| LOAD       | 7002    | DONE FLAG: 0 return indicates not done          |

| LOAD       | 7003    | VALUE : low order 4 bits of A/D value           |

| LOAD       | 7004    | VALUE : high order bits of A/D value            |

| STORE      | 7005    | RESET : reset A/D converter, clear flag         |

A routine to select a line (the line number in the AC to start) and read the value of the analog signal into D5, D6 is as follows:

| 1  | READ: | LDI | 7000 | ;LOAD ADDRESS OF A/D INTO DP      |

|----|-------|-----|------|-----------------------------------|

| 2  |       | SAD |      | SEND LINE NUMBER                  |

| 3  |       | IDP |      | INCREMENT TO START FUNCTION       |

| 4  |       | SAD |      | ; SEND START (DATA IS IGNORED)    |

| 5  |       | IDP |      | INCREMENT TO ADDRESS OF DONE FLAG |

| 6  | WAIT: | LAD |      | JLOAD FLAG                        |

| 7  |       | J₹  | WAIT | JUMP BACK IF ZERO                 |

| 8  |       | IDP |      | IT IS READY, INCREMENT TO VALUE   |

| 9  |       | LAD |      | JLOAD LOW ORDER BITS              |

| 10 |       | SAR | D5   | SAVE THEM                         |

| 11 |       | IDP |      | ; INCREMENT TO NEXT NIBBLE        |

| 12 |       | LAD |      | ; LOAD NEXT NIBBLE                |

| 13 |       | SAR | D6   | ; AND STORE IT                    |

The following is a step-by-step analysis of this program:

- 1. The data pointer is loaded with the address 7000, the first address assigned to the A/D subsystem.

- The SAD instruction normally stores the AC in the memory location specified by the data pointer, but connected to address 7000 is not memory but the multiplexer of the A/D. The 4 bits sent over the data bus by the SAD instruction select the proper line.

- 3. The IDP adds 1 to the DP. The DP now specifies location 7001.

- Another SAD selects the start function in the A/D. The data from the AC which the CPU places on the data bus are ignored by the A/D. The start pulse initiates conversion of the analogue signal.

FIG. 3. A/D CONVERTER SUBSYSTEM

- 5. Following this IDP, the DP contains the address of the A/D DONE flag.

- The LAD instruction reads the contents of the A/D DONE flag into the AC (i.e., when the A/D detects address 7002, it places the flag on the data bus).

- If the value read into the AC from the data bus is 0 the JZ test (jump if zero AC) is successful, control returns